- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Ano ang Proseso ng CMP

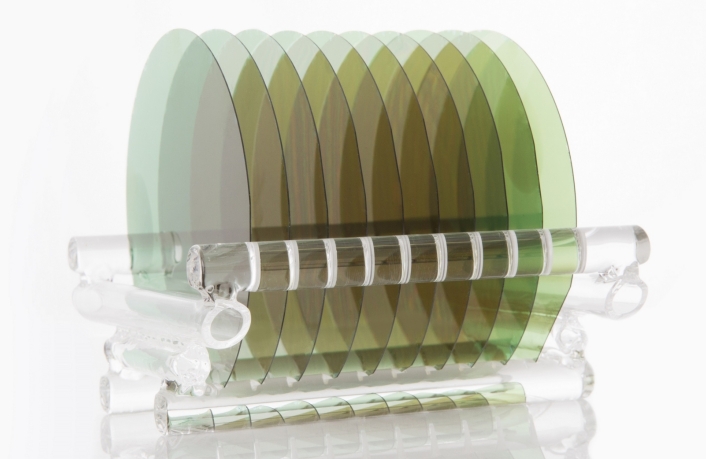

Sa paggawa ng semiconductor, ang atomic-level na flatness ay karaniwang ginagamit upang ilarawan ang global flatness ngostiya, na may yunit ng nanometer (nm). Kung ang kinakailangan sa pandaigdigang flatness ay 10 nanometer (nm), katumbas ito ng maximum na pagkakaiba sa taas na 10 nanometer sa isang lugar na 1 metro kuwadrado (10nm global flatness ay katumbas ng pagkakaiba sa taas sa pagitan ng alinmang dalawang punto sa Tiananmen Square na may isang area na 440,000 square meters na hindi hihigit sa 30 microns.) At ang pagkamagaspang sa ibabaw nito ay mas mababa sa 0.5um (kumpara sa isang buhok na may diameter na 75 microns, ito ay katumbas ng isang 150,000th ng isang buhok). Ang anumang hindi pagkakapantay-pantay ay maaaring magdulot ng short circuit, circuit break o makaapekto sa pagiging maaasahan ng device. Ang high-precision na kinakailangan sa flatness na ito ay kailangang maabot sa pamamagitan ng mga proseso tulad ng CMP.

Prinsipyo ng proseso ng CMP

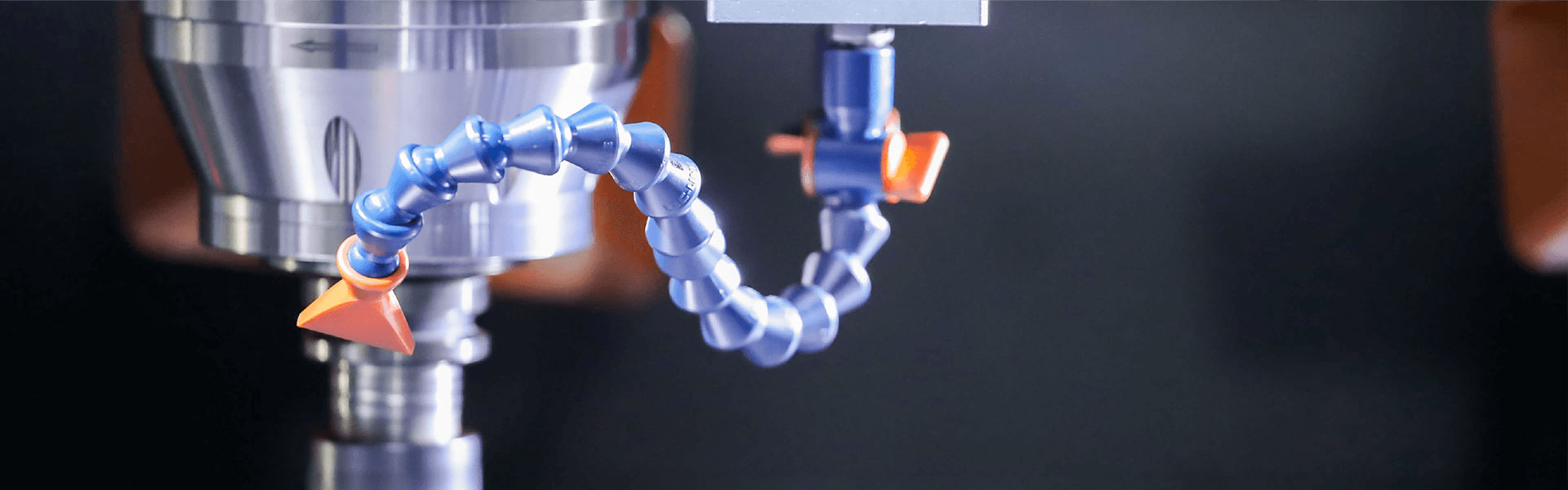

Ang Chemical mechanical polishing (CMP) ay isang teknolohiyang ginagamit upang patagin ang ibabaw ng wafer sa panahon ng paggawa ng semiconductor chip. Sa pamamagitan ng kemikal na reaksyon sa pagitan ng polishing liquid at ng wafer surface, nabuo ang isang layer ng oxide na madaling hawakan. Ang ibabaw ng layer ng oxide ay tinanggal sa pamamagitan ng mekanikal na paggiling. Matapos ang maramihang mga kemikal at mekanikal na aksyon ay ginawa nang halili, isang pare-pareho at patag na ibabaw ng ostiya ay nabuo. Ang mga chemical reactant na inalis mula sa ibabaw ng wafer ay natutunaw sa dumadaloy na likido at inaalis, kaya ang proseso ng pag-polish ng CMP ay may kasamang dalawang proseso: kemikal at pisikal.