- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Sic gilid singsing

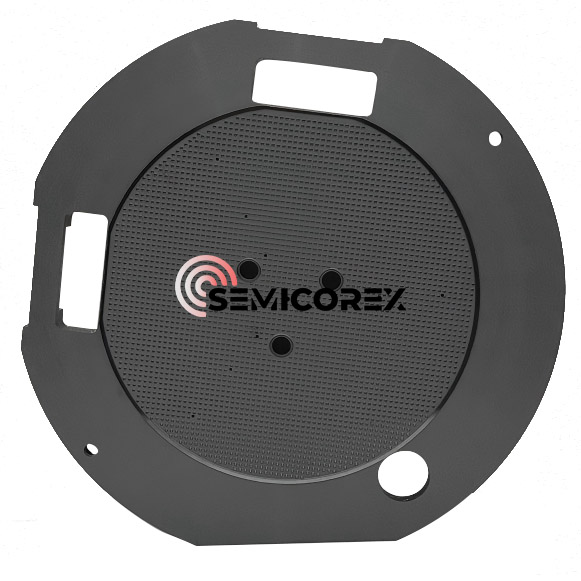

Ang Semicorex CVD SIC Edge Ring ay isang sangkap na may mataas na pagganap na plasma na idinisenyo upang mapahusay ang pagkakapareho ng etching at protektahan ang mga wafer na gilid sa pagmamanupaktura ng semiconductor. Piliin ang Semicorex para sa hindi katumbas na kadalisayan ng materyal, katumpakan ng engineering, at napatunayan na pagiging maaasahan sa mga advanced na proseso ng proseso ng plasma.*

Magpadala ng Inquiry

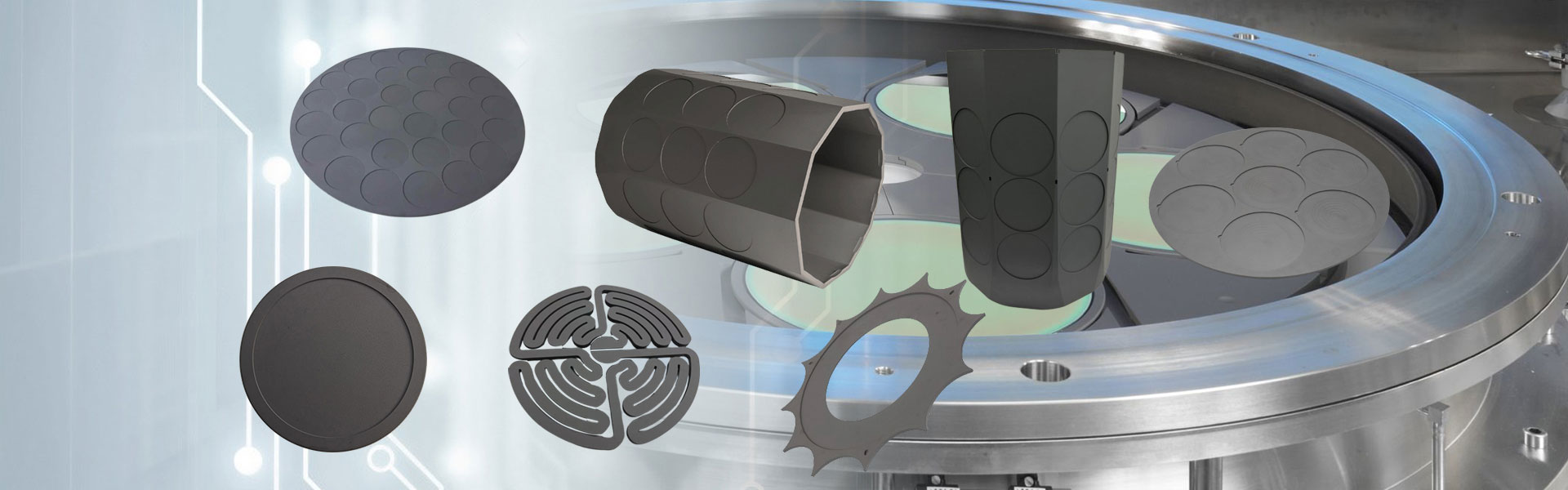

Ang Semicorex sic Edge Ring, na ginawa sa pamamagitan ng Chemical Vapor Deposition (CVD) silikon carbide (SIC), ay kumakatawan sa isang kritikal na aspeto ng semiconductor na katha, na partikular na naglalaro ng isang mahalagang papel sa proseso ng katha sa mga silid ng plasma etching. Ang singsing sa gilid ay matatagpuan sa paligid ng panlabas na gilid ng electrostatic chuck (ESC) sa panahon ng proseso ng plasma etching at may parehong aesthetic at functional na relasyon sa wafer in-process.

Sa pagmamanupaktura ng semiconductor integrated circuit (IC), ang pantay na pamamahagi ng plasma ay kritikal ngunit ang mga depekto sa gilid ng wafer ay mahalaga upang mapanatili ang mataas na ani sa panahon ng paggawa ng mga pamamaraan ng IB at IBF, bilang karagdagan sa maaasahang mga de -koryenteng pagtatanghal ng iba pang mga IC. Mahalaga ang singsing ng SIC Edge sa pamamahala ng parehong pagiging maaasahan ng plasma sa gilid ng wafer habang nagpapatatag ng mga hangganan ng hangganan ng wafer sa silid nang hindi pinapahalagahan ang dalawa bilang mga variable na nakikipagkumpitensya.

Habang ang proseso ng plasma etching na ito ay isinasagawa sa mga wafer, ang mga wafer ay malantad sa pambobomba mula sa mga ion na may mataas na enerhiya, na may mga reaktibong gas na nag-aambag upang ilipat ang mga pattern ng electively. Ang mga kundisyong ito ay lumikha ng mga proseso ng density ng high-energy na maaaring negatibong nakakaapekto sa pagkakapareho at kalidad ng wafer na gilid kung hindi ito pinamamahalaan nang tama. Ang singsing sa gilid ay maaaring magkasama sa konteksto ng pagproseso ng wafer at habang ang generator ng electrified plasma ay nagsisimulang ilantad ang mga wafer, ang gilid ng singsing ay sumisipsip at muling ibigay ang enerhiya sa gilid ng silid at palawakin ang epektibong kahusayan ng electric field mula sa generator hanggang sa gilid ng ESC. Ang diskarte na nagpapatatag na ito ay ginagamit sa iba't ibang paraan, kabilang ang pagbabawas ng dami ng pagtagas ng plasma at pagbaluktot malapit sa gilid ng hangganan ng wafer na maaaring humantong sa burnout-failure ng gilid.

Sa pamamagitan ng pagtaguyod ng isang balanseng kapaligiran ng plasma, ang singsing ng SIC Edge ay nakakatulong na mabawasan ang mga epekto ng micro-loading, maiwasan ang over-etching sa wafer periphery, at palawakin ang buhay ng parehong mga wafer at mga sangkap ng silid. Pinapayagan nito ang mas mataas na pag-uulit ng proseso, nabawasan ang kakulangan, at mas mahusay sa buong-wafer na pagkakapareho-mga susi na sukatan sa paggawa ng mataas na dami ng semiconductor.

Ang mga discontinuities ay kaisa sa bawat isa, na ginagawang mas mahirap ang proseso ng pag -optimize sa gilid ng wafer. Halimbawa, ang mga de -koryenteng discontinuities ay maaaring maging sanhi ng pagbaluktot ng morphology ng kaluban, na nagiging sanhi ng pagbabago ng mga ions ng insidente, kaya nakakaapekto sa pagkakapareho ng etching; Ang patlang na hindi pagkakapareho ng temperatura ay maaaring makaapekto sa rate ng reaksyon ng kemikal, na nagiging sanhi ng rate ng gilid ng etching na lumihis mula sa gitnang lugar. Bilang tugon sa mga hamon sa itaas, ang mga pagpapabuti ay karaniwang ginawa mula sa dalawang aspeto: pag -optimize ng disenyo ng kagamitan at pagsasaayos ng parameter ng proseso.

Ang pokus na singsing ay isang pangunahing sangkap upang mapabuti ang pagkakapareho ng wafer edge etching. Naka -install ito sa paligid ng gilid ng wafer upang mapalawak ang lugar ng pamamahagi ng plasma at mai -optimize ang morpolohiya ng sheath. Sa kawalan ng isang singsing na pokus, ang pagkakaiba sa taas sa pagitan ng gilid ng wafer at ang elektrod ay nagiging sanhi ng pagbaluktot ng kaluban, na nagiging sanhi ng pagpasok ng mga ions sa isang di-pantay na anggulo.

Ang mga pag -andar ng singsing ng pokus ay kasama ang:

• Ang pagpuno ng pagkakaiba sa taas sa pagitan ng gilid ng wafer at ang elektrod, na ginagawang flatter ang kaluban, tinitiyak na ang mga ions ay bumomba sa ibabaw ng wafer nang patayo, at pag -iwas sa pagpapalawak ng etching.

• Pagbutihin ang pagkakapareho ng etching at bawasan ang mga problema tulad ng labis na gilid ng etching o tilted etching profile.

Mga kalamangan sa materyal

Ang paggamit ng CVD sic bilang base material ay nag -aalok ng maraming mga pakinabang sa tradisyonal na mga ceramic o coated na materyales. Ang CVD SIC ay kemikal na walang kabuluhan, thermally stable, at lubos na lumalaban sa pagguho ng plasma, kahit na sa agresibong fluorine- at mga chemistries na batay sa klorin. Ang mahusay na mekanikal na lakas at dimensional na katatagan ay matiyak ang mahabang buhay ng serbisyo at mababang henerasyon ng butil sa ilalim ng mga kondisyon ng pagbibisikleta ng mataas na temperatura.

Bukod dito, ang ultra-pure at siksik na microstructure ng CVD SIC ay binabawasan ang panganib ng kontaminasyon, na ginagawang perpekto para sa mga ultra-clean na pagproseso ng mga kapaligiran kung saan kahit na ang mga impurities sa bakas ay maaaring makaapekto sa ani. Ang pagiging tugma nito sa umiiral na mga platform ng ESC at mga pasadyang geometry ng silid ay nagbibigay -daan para sa walang tahi na pagsasama na may advanced na 200mm at 300mm etching tool.